# Semiconductor chip design for low noise radiation measurement

Habin Kim, and Inyong Kwon\*

Department of Radiological convergence Engineering, Yonsei University, Korea E-mail: vinny6780@yonsei.ac.kr \*Corresponding author: ikwon@yonsei.ac.kr

\**Keywords* : Charge-Sensitive Amplifier (CSA), Low-Noise Analog Design, Spectroscopy and Radiation Measurement, Frequency Response Analysis

### 1. Introduction

Charge Sensitive Amplifiers (CSAs) are pivotal in applications such as high-resolution spectroscopy, particle physics, and radiation detection. They convert charge signals from detectors into voltage signals, facilitating precise measurement and analysis. Designing CSAs involves challenges like minimizing noise while maintaining high charge sensitivity. Variations in detector capacitance and environmental noise can further degrade performance, necessitating robust design strategies.

This study aims to develop a CSA optimized for low noise and high stability under varying operational conditions. The design focuses on minimizing Equivalent Noise Charge (ENC), ensuring stable charge-to-voltage conversion, and incorporating techniques to enhance overall performance. The proposed CSA will undergo comprehensive simulations to assess its feasibility in practical applications.

### 2. CSA Design Considerations

The CSA is designed to balance noise performance, charge sensitivity, and environmental stability. A lownoise Junction Field-Effect Transistor (JFET) is utilized at the input stage to suppress thermal and flicker noise. The feedback network comprises a carefully selected capacitor and resistor combination to optimize charge integration while mitigating noise effects. The CSA aims for a charge-to-voltage conversion gain of approximately 1 mV/fC, allowing precise charge measurement over a dynamic range of 1 fC to 10 pC.

To enhance robustness, transistor sizing strategies, such as increased channel width, are applied to reduce threshold voltage shifts and mitigate noise degradation under varying conditions. The expected ENC is designed to remain below 100 electrons, ensuring compatibility with high-resolution spectroscopy applications.

The CSA layout is optimized to ensure signal integrity, even in environments where external factors like thermal noise and stray capacitance could impact circuit behavior.

### 3. Simulation Plan

To verify the proposed CSA design, simulations will evaluate the ENC across different operating conditions, ensuring compliance with high-resolution spectroscopy requirements. Transient response simulations will assess the CSA's ability to process charge pulses accurately, focusing on rise time (< 10 ns), fall time, and pulse shape fidelity.

Frequency response measurements will confirm that the CSA's bandwidth, targeted at 10 MHz, aligns with expected detector signal frequencies, preserving signal integrity. An electrical analysis of the circuit will be conducted to evaluate gain stability and noise performance.

## 4. Anticipated Results

The CSA is expected to demonstrate high charge sensitivity (~1 mV/fC) and low noise performance (ENC < 100 electrons), meeting stringent spectroscopy requirements. The design should exhibit stable charge-to-voltage conversion with less than 0.1% nonlinearity, ensuring accurate signal representation [1].

Additionally, the power consumption of the CSA is projected to remain below 5 mW, ensuring energy efficiency for extended operation in spectroscopy and radiation measurement applications [2].

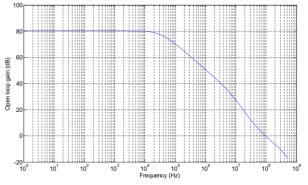

Fig. 1 illustrates the open-loop gain plot of the conventional CSA, showing a DC gain slightly above 80 dB and a gain-bandwidth product of approximately 345 MHz. These results indicate that the CSA maintains stable gain characteristics while preserving a wide frequency response, crucial for spectroscopy applications [3].

An electrical analysis of the circuit will be conducted, and the findings will be presented at an upcoming conference.

**Fig. 1** Open-loop gain plot of the conventional CSA, showing a DC gain slightly above 80 dB and a gain-bandwidth product of ~345 MHz [3].

#### Acknowledgements

This work was supported in part by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry & Energy (MOTIE) of the Republic of Korea (No. 20214000000070) and the Technology development Program (RS-2023-00322102) funded by the Ministry of SMEs and Startups (MSS, Korea).

The EDA tool was supported by the IC Design Education Center (IDEC), Korea

#### REFERENCES

[1] A. Takeda, T.G. Tsuru, T. Tanaka, H. Uchida, H. Matsumura, Y. Arai, K. Mori, Y. Nishioka, R. Takenaka, and T. Kohmura, "Improvement of Spectroscopic Performance using a Charge-sensitive Amplifier Circuit for an X-Ray Astronomical SOI Pixel Detector," Journal of Instrumentation, Vol. 10, June 2015. DOI: 10.1088/1748-0221/10/06/C06005

[2] P. Födisch, M. Berthel, B. Lange, T. Kirschke, W. Enghardt, and P. Kaever, "Charge-sensitive front-end electronics with operational amplifiers for CdZnTe detectors," Journal of Instrumentation, Vol. 11, September 2016. DOI: 10.1088/1748-0221/11/09/T09001

[3] Mohammad Beikahmadi and Shahriar Mirabbasi, "A low-power low-noise CMOS charge-sensitive amplifier for capacitive detectors," 2011 IEEE 9th International New Circuits and Systems Conference (NEWCAS), Bordeaux, France, 26-29 June 2011, DOI: 10.1109/NEWCAS.2011.5981267