## VIS

## A Usability Review of a Model Checker VIS for the Verification of NPP I&C System Safety Software

## **Abstract**

This paper discusses the usability of a model checker VIS in the verification of safety software of NPP I&C systems. The software development environment exemplified in this paper is for PLC and ESF-CCS which are being developed in KNICS project. In this environment, STATEMATE is used in requirement analysis and design phases. PLC is expected to be implemented using C

language and an assembly language because it has many interfaces with hardware like CPU, I/O devices, communication devices. ESF-CCS is supposed to be developed in terms of PLC programming languages which are defined in IEC 61131-3 standard. In this case, VIS proved to be very useful through the review. We are also able to expect greater usability of VIS if we further develop the techniques for code abstraction and automatic translation from code to verilog, which is the input of VIS.

1.

(Embedded) (Real-time) 가 . (Non-deterministic) (Multi-process)

(Non-determinism) (Deadlock) 가

(Verification and Validation) 가 ... IEEE Std. 7-4.3.2[1] IEEE Std 1012[2] IEEE

Std 1074[3]

AECL 가 가

, ,

가

. 가

,

•

VIS가

가 .

## 2. VIS

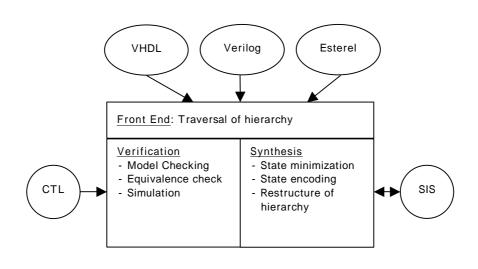

VIS(Verification Interacting with Synthesis) , , ,

fair CTL , (Combinational and sequential equivalence checking) , (Hierarchical synthesis)

. 1 VIS .

1. VIS

VIS BLIF-MV BLIF\_MV vI2mv

. VIS가 Verilog Verilog

. vI2mv가 Verilog BLIF-MV

```

가

CTL

CTL

(path)

가

CTL

(Boolean connective),

(Path quantifier: A,E)

(Temporal modality:

F,X,G,U)

(Formula)

가

" q"

" q"

", G

Χ

, U

AG safe가 q

(G)

safe

(A)

AF safe 가 q

(A)

, q

, EG safe가 q

(F)가 safe

(G)가 safe

(E)

q

EF safe가 q

(E)

, q

(F)가 safe

가

. CTL

Fair

path)

. Fair

fair

CTL

fairness

Fair CTL

, VIS

fair CTL

3.

(Programmable Logic

Controller,

PLC)

(Engineered Safety Feature

Actuation System)

VIS

가

. PLC

가

가

가

가

가

```

(Reactive System) .

가

가

3.1. PLC

Statechart

Statechart STATEMATE[5] 가

. STATEMATE가 Activity Chart Statechart

3.2.

STATEMATE Activity Chart Statechart Module Chart

. Activity

Chart Statechart , Module Chart

4. VIS

4.1.

3.3. STATEMATE가 가

PLC

. PLC , C PLC

Ladder Diagram, Function Block Diagram

PLC .

STATEMATE .

STATEMATE가 Model Checker/Model Certifier STATEMATE

. Model Checker/Model Certifier가 VIS

. , STATEMATE

, VIS

PLC VIS STATEMATE Model Checker/Model Certifier Model Checker/Model Certifier STATEMATE VIS . Model Checker가 . Model Certifier 가 . VIS (Dead Code Analysis) (Robustness Check) 4.2. PLC STATEMATE VIS VIS Verilog CTL . Statechart가 VIS , STATEMATE VIS 가 Verilog VIS 가 가 CTL VIS가 VIS가 4.3. PLC PLC С . PLC 가 가 Verilog가 . Verilog가 PLC VIS가 PLC VIS Verilog Front-end 가 С PLC 가 Verilog

```

가

가

가

가

가

가

가

가

가

. VIS

Verilog

4.4.

PLC

VIS

. PLC

IEC 61131-3

. IEC 61131-3

가 PLC

Sequential Function Chart(SFC)

. 가

(Syntax)

(Semantics)

Ladder Diagram(LD),

Function Block Diagram(FBD), Structured Text(ST) Instruction List(IL)

LD

. FBD

. ST

PLC

. IL

. SFC

. SFC

PLC

- PLC

(Operational Semantics)

PLC

, SFC

SFC

가

4.4.1. PLC

PLC

가

가

(Sub-program)

. SFC

PLC

SFC

```

SFC . ST LD PLC 4.4.2. SFC SFC 가 가 가 4.4.3. LD LD 가 LD LD 가 . LD 가 4.4.4. ST ST . ST , PLC 가 PLC . VIS가 PLC 5. 가 가 VIS가 STATEMATE

PLC

VIS

VIS 가 , VIS

(1)

가

(2) VIS

- [1] IEEE, "IEEE Standard Criteria for Digital Computers in Safety Systems of Nuclear Power Generating Stations", IEEE Std 7-4.3.2-1993, Sep. 15, 1993.

- [2] IEEE, "IEEE Standard for Software Verification and Validation Plans", ANSI/IEEE Std. 1012-1986, Feb. 10, 1987.

- [3] IEEE, "Standard for Developing Software Life Cycle Processes," IEEE Std. 1074-1997.

- [4] R. Alur and T. Henzinger . VIS: A system for Verification and Synthesis", The VIS Group, In the Proceedings of the 8th International Conference on Computer Aided Verification, p428-432, Springer Lecture Notes in Computer Science, #1102, New Brunswick, NJ, July 1996.

- [5] David Harel and Ammon Naamad, The STATEMATE Semantics of Statecharts, ACM Trans. Soft. Eng. Method. Oct. 1996.